Оптимізація виходу прототипів у виробництві напівпровідників: Як передові технології революціонізують виробництво на ранніх стадіях і забезпечують конкурентні переваги

- Вступ: Критична роль виходу прототипів у успіху напівпровідників

- Основні виклики досягнення високого виходу прототипів

- Передові технології контролю та моніторингу процесів

- Методи на основі даних: Використання ШІ та машинного навчання для покращення виходу

- Проектування для виробництва: Інтеграція міркувань виходу на ранніх етапах

- Аналіз кореневих причин і стратегії зменшення дефектів

- Кейс-стадії: Реальні успіхи в оптимізації виходу прототипів

- Майбутні тенденції: Нові технології, що формують покращення виходу

- Висновок: Найкращі практики для підтримки відмінності виходу прототипів

- Джерела та посилання

Вступ: Критична роль виходу прототипів у успіху напівпровідників

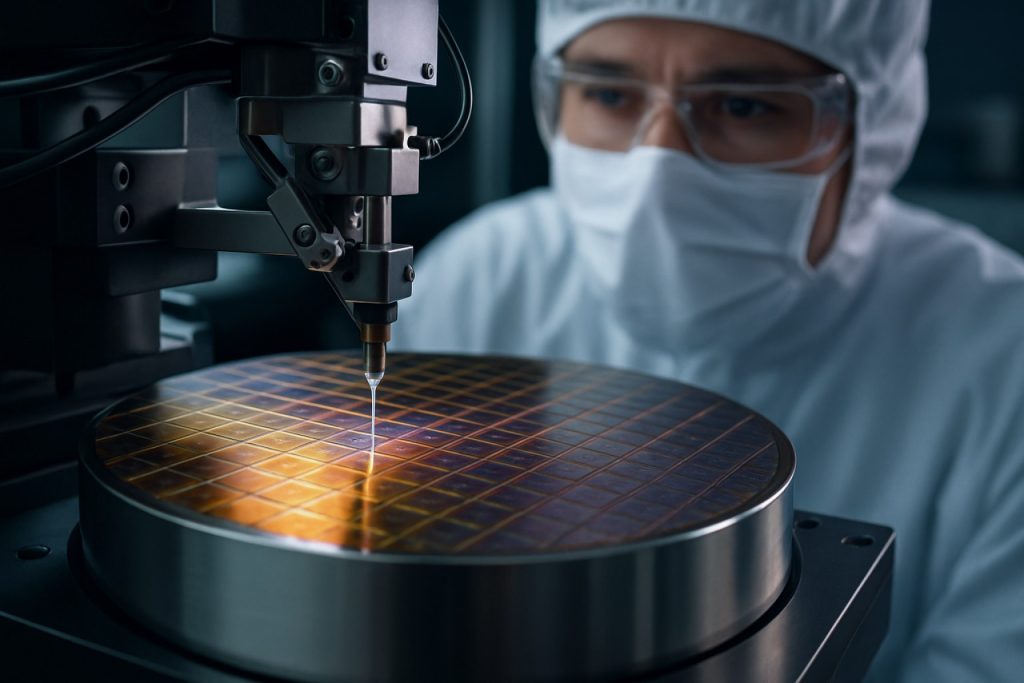

У жорстко конкурентному середовищі виробництва напівпровідників вихід, досягнутий під час прототипування, є вирішальним фактором, що визначає як технічну, так і комерційну життєздатність нових пристроїв. Вихід прототипу відноситься до частки функціональних чіпів, виготовлених з початкової партії пластин, що слугує важливим показником зрілості процесу та надійності дизайну. Високий вихід прототипів прискорює вихід на ринок, знижує витрати на розробку та підвищує ймовірність успішного масового виробництва, тоді як низький вихід може сигналізувати про фундаментальні проблеми дизайну або процесу, які можуть загрожувати запуску продукту або його прибутковості.

Важливість оптимізації виходу прототипів зросла в міру ускладнення архітектур пристроїв та зменшення розмірів елементів до нанометрового масштабу. Раннє виявлення та усунення факторів, що знижують вихід, таких як недоліки дизайну, варіабельність процесу та дефекти матеріалів, є необхідними для уникнення витратних ітерацій та затримок. Сучасні інструменти аналізу виходу, управління процесами на основі даних та тісна співпраця між командами дизайну та виробництва наразі є стандартними практиками для максимізації виходу прототипів і забезпечення плавного переходу до обсягового виробництва. Як підкреслює компанія Taiwan Semiconductor Manufacturing Company (TSMC), раннє навчання виходу не лише покращує ефективність виробництва, але й надає цінний зворотний зв’язок для оптимізації дизайну та вдосконалення процесів.

Зрештою, здатність оптимізувати вихід прототипів є ключовим фактором для компаній у сфері напівпровідників, безпосередньо впливаючи на якість продукції, структуру витрат та конкурентоспроможність на ринку. Оскільки галузь продовжує розширювати межі технологій, стратегічний акцент на оптимізації виходу прототипів залишиться центральним для досягнення інновацій та комерційного успіху.

Основні виклики досягнення високого виходу прототипів

Досягнення високого виходу прототипів у виробництві напівпровідників стикається з унікальними викликами, які відрізняються від тих, що виникають у масовому виробництві. Однією з основних перешкод є варіабельність процесу, яка більш виражена під час етапу прототипування через часті зміни дизайну, недозрілі рецепти процесів та обмежений статистичний контроль процесів. Ці фактори можуть призвести до непослідовності в продуктивності пристроїв та підвищення рівня дефектів, що ускладнює досягнення цільових показників виходу, необхідних для економічної розробки SEMI.

Іншим значним викликом є обмежена доступність тестових структур та даних моніторингу. На відміну від зрілих виробничих ліній, прототипні запуски часто не мають всеосяжного вбудованого метрологічного та дефектного контролю, що ускладнює швидкий аналіз кореневих причин та коригувальні дії. Ця нестача даних може затримати виявлення систематичних факторів, що знижують вихід, таких як невідповідність літографії, відхилення профілю травлення або події забруднення TSMC.

Крім того, інтеграція нових матеріалів та архітектур пристроїв у прототипах вводить непередбачувані механізми відмови. Це можуть бути підвищена чутливість до стресу, викликаного процесом, нові дефекти на межах або непередбачувані взаємодії між етапами процесу. Відсутність історичних даних про відмови для цих нововведень ще більше ускладнює навчання та оптимізацію виходу Intel.

Нарешті, тиск на швидкість виходу на ринок часто змушує прискорити цикли розробки, зменшуючи можливість ретельного охарактеризування та оптимізації процесів. Це може призвести до субоптимальних вікон процесів та підвищеної початкової щільності дефектів, що ще більше ускладнює зусилля з покращення виходу під час критичного етапу прототипування.

Передові технології контролю та моніторингу процесів

Передові технології контролю процесів (APC) та моніторингу є ключовими для оптимізації виходу прототипів під час виробництва напівпровідників, де варіабельність процесу на ранніх етапах може значно вплинути на продуктивність пристроїв і витрати. Системи APC інтегрують збір даних у реальному часі з контролюючими стратегіями зворотного та попереднього зв’язку для підтримки параметрів процесу в межах суворих допусків, тим самим знижуючи рівень дефектів і підвищуючи вихід. Ці системи використовують датчики, метрологічні інструменти та алгоритми машинного навчання для виявлення відхилень та прогнозування потенційних факторів, що знижують вихід, ще до їх прояву у фінальному продукті.

Ключові методи моніторингу включають вбудовану метрологію, яка надає негайний зворотний зв’язок про критичні розміри, товщину плівки та точність накладення, а також системи виявлення та класифікації дефектів (FDC), які постійно аналізують сигнали обладнання та процесу на предмет аномалій. Запроваджуючи статистичний контроль процесів (SPC) і віртуальну метрологію, виробники можуть виявляти тонкі зсуви процесу та збої обладнання, які можуть бути не очевидними під час традиційної перевірки в кінці лінії. Цей проактивний підхід дозволяє швидко вживати коригувальні заходи, мінімізуючи поширення дефектів через подальші етапи процесу.

Останні досягнення в APC включають інтеграцію штучного інтелекту та аналітики великих даних, що дозволяє здійснювати прогнозне обслуговування та адаптивне налаштування процесів. Ці технології сприяють швидкому виявленню кореневих причин втрати виходу, особливо в контексті складного, багатоступеневого виготовлення прототипів. В результаті виробники можуть досягати вищого виходу з першого проходу, зменшувати час циклу та прискорювати перехід від прототипу до обсягового виробництва. Для отримання додаткових деталей зверніться до ресурсів SEMI та Applied Materials.

Методи на основі даних: Використання ШІ та машинного навчання для покращення виходу

Методи на основі даних, зокрема ті, що використовують штучний інтелект (ШІ) та машинне навчання (МН), трансформують оптимізацію виходу прототипів у виробництві напівпровідників. Використовуючи величезні обсяги даних про процеси, обладнання та тестування, моделі ШІ/МН можуть виявляти тонкі закономірності та кореляції, які можуть бути пропущені традиційними статистичними методами. Ці висновки дозволяють рано виявляти фактори, що знижують вихід, проводити аналіз кореневих причин та прогнозне обслуговування, що є критично важливим для покращення виходу прототипів.

Однією з ключових застосувань є використання алгоритмів навчання з наглядом для прогнозування виходу пластини або чіпа на основі параметрів процесу та даних вбудованої метрології. Навчаючи моделі на історичних даних, виробники можуть прогнозувати результати виходу для нових прототипів і проактивно коригувати налаштування процесу для зменшення ризиків. Техніки навчання без нагляду, такі як кластеризація та виявлення аномалій, допомагають виявляти раніше невідомі джерела варіацій або поведінки аутлайерів у процесі виготовлення, що дозволяє здійснювати цілеспрямовані коригувальні дії.

Системи класифікації дефектів на основі ШІ, які працюють на основі глибокого навчання, можуть швидко аналізувати зображення перевірки високої роздільної здатності, щоб відрізнити безпечні дефекти від тих, що обмежують вихід, зменшуючи кількість помилкових спрацьовувань та прискорюючи виявлення кореневих причин. Крім того, досліджується використання навчання з підкріпленням для оптимізації стратегій контролю процесів у реальному часі, адаптуючись до змінних умов і мінімізуючи втрати виходу під час ранніх прототипних запусків.

Інтеграція ШІ/МН у платформи управління виходом підтримується провідними компаніями та консорціумами, такими як SEMI та Taiwan Semiconductor Manufacturing Company (TSMC), які виступають за стандартизовані формати даних та спільну аналітику. Оскільки методології на основі даних розвиваються, очікується, що вони відіграватим дедалі центральнішу роль у прискоренні виходу та зменшенні часу виходу на ринок для просунутих прототипів напівпровідників.

Проектування для виробництва: Інтеграція міркувань виходу на ранніх етапах

Інтеграція міркувань виходу на найраніших етапах дизайну напівпровідників, що зазвичай називається проектуванням для виробництва (DfM), є критично важливою стратегією для оптимізації виходу прототипів. Вбудовуючи міркування виходу в процес дизайну, інженери можуть проактивно вирішувати потенційні проблеми виробництва, зменшуючи витратні ітерації та прискорюючи вихід на ринок. DfM передбачає тісну співпрацю між командами дизайну та процесу для виявлення та усунення джерел втрат виходу, таких як ефекти, залежні від макета, варіабельність процесу та чутливість до дефектів.

Ключові практики DfM включають використання передових правил дизайну, які враховують обмеження літографії, контроль критичних розмірів та варіабельність вікна процесу. Наприклад, регулярність макета та надмірність можуть бути включені для підвищення толерантності до дефектів, тоді як критичні області, схильні до систематичних дефектів, можуть бути мінімізовані через ретельне планування та маршрутизацію. Крім того, використовуються інструменти моделювання та прогностичні моделі для оцінки виробничої спроможності вибору дизайну до виготовлення фізичних прототипів, що дозволяє рано виявляти фактори, що знижують вихід.

Впровадження методологій DfM показало значне покращення виходу з першого проходу, особливо в міру зменшення геометрії пристроїв та збільшення складності процесів. Галузеві стандарти та рекомендації, такі як ті, що надаються SEMI (Semiconductor Equipment and Materials International) та IEEE (Інститут інженерів електротехніки та електроніки), пропонують рамки для інтеграції DfM у життєвий цикл розробки напівпровідників. Зрештою, рання оптимізація виходу через DfM не лише підвищує ймовірність успіху прототипів, але й сприяє зниженню витрат на виробництво та покращенню надійності продукції.

Аналіз кореневих причин і стратегії зменшення дефектів

Аналіз кореневих причин (RCA) є основою для оптимізації виходу прототипів у виробництві напівпровідників, оскільки він систематично виявляє та вирішує основні фактори, що сприяють втраті виходу. Складність процесів напівпровідників — від фотолітографії, травлення, осадження до упаковки — означає, що дефекти можуть виникати з безлічі джерел, включаючи збої обладнання, домішки в матеріалах, варіації процесу та людські помилки. Ефективний RCA використовує комбінацію статистичного контролю процесів (SPC), аналізу режимів відмов та їх наслідків (FMEA) та передової аналітики даних для відстеження дефектів до їхнього походження, що дозволяє вживати цілеспрямовані коригувальні дії.

Стратегії зменшення дефектів тісно пов’язані з висновками, отриманими з RCA. Наприклад, коли повторюване забруднення частками відстежується до конкретного інструменту або етапу процесу, виробники можуть впроваджувати цілеспрямовані графіки обслуговування, модернізувати системи фільтрації або змінювати рецепти процесів для усунення проблеми. Крім того, впровадження моніторингу в реальному часі та алгоритмів машинного навчання дозволяє рано виявляти зсуви процесу та аномалії, що ще більше знижує частоту дефектів, що впливають на вихід. Крос-функціональні команди, до складу яких входять інженери процесів, техніки обладнання та фахівці з контролю якості, співпрацюють для впровадження та перевірки коригувальних заходів, забезпечуючи, щоб поліпшення зберігалися під час наступних запусків прототипів.

Фреймворки безперервного поліпшення, такі як Six Sigma та Total Quality Management (TQM), часто інтегруються в ініціативи зменшення дефектів, сприяючи культурі проактивного вирішення проблем та ухвалення рішень на основі даних. Систематично вирішуючи кореневі причини та впроваджуючи надійні стратегії зменшення дефектів, виробники напівпровідників можуть значно підвищити вихід прототипів, прискорити вихід на ринок та знизити витрати на розробку, як підкреслює SEMI та Texas Instruments.

Кейс-стадії: Реальні успіхи в оптимізації виходу прототипів

Декілька виробників напівпровідників досягли значних поліпшень в оптимізації виходу прототипів через інтеграцію передової аналітики, контролю процесів та крос-функціональної співпраці. Наприклад, компанія Intel Corporation впровадила алгоритми машинного навчання для аналізу моделей дефектів та прогнозування факторів, що обмежують вихід, на ранніх етапах розробки процесу. Цей підхід дозволив швидко виявляти та усувати кореневі причини, що призвело до повідомленого зростання виходу з першого проходу на 15% для нових процесів.

Аналогічно, компанія Taiwan Semiconductor Manufacturing Company (TSMC) впровадила статистичний контроль процесів (SPC) в реальному часі та автоматизовані зворотні зв’язки на своїх пілотних лініях. Постійно моніторячи критичні параметри процесу та корелюючи їх з електричними тестовими результатами, TSMC зменшила час циклу прототипів і покращила темпи підвищення виходу, прискорюючи вихід на ринок для новітніх технологій.

Ще одним помітним прикладом є Samsung Electronics, яка використовувала цифрові двійники та віртуальні моделі виготовлення для моделювання варіацій процесу та оптимізації стратегій проектування для виробництва (DFM). Цей цифровий підхід дозволив Samsung проактивно вирішувати потенційні фактори, що знижують вихід, ще до фізичного прототипування, що призвело до вищих початкових виходів та зниження витрат на розробку.

Ці кейс-стадії підкреслюють цінність методів на основі даних, раннього виявлення дефектів та міждисциплінарної команди в досягненні оптимізації виходу прототипів. Успіхи лідерів галузі демонструють, що інвестиції в передові технології контролю процесів та прогнозну аналітику можуть забезпечити вимірювані поліпшення виходу, економічної ефективності та якості продукції в виробництві напівпровідників.

Майбутні тенденції: Нові технології, що формують покращення виходу

Майбутнє оптимізації виходу прототипів у виробництві напівпровідників формується завдяки злиттю нових технологій, які обіцяють революціонізувати виявлення дефектів, контроль процесів та аналітику даних. Однією з найзначніших тенденцій є інтеграція штучного інтелекту (ШІ) та машинного навчання (МН) у системи управління виходом. Ці технології дозволяють здійснювати реальний аналіз величезних наборів даних, що генеруються під час виготовлення пластин, що дозволяє здійснювати прогнозне обслуговування, швидкий аналіз кореневих причин та адаптивні налаштування процесів, які мінімізують втрати виходу Taiwan Semiconductor Manufacturing Company.

Ще одним трансформаційним розвитком є впровадження передових метрологічних та інспекційних інструментів, таких як системи високої роздільної здатності електронного променя та оптичної інспекції. Ці інструменти забезпечують безпрецедентну чутливість до субнанометрових дефектів, що дозволяє раніше виявляти та класифікувати аномалії, що обмежують вихід, під час етапу прототипування KLA Corporation. Крім того, використання цифрових двійників — віртуальних копій виробничих процесів — дозволяє інженерам моделювати та оптимізувати параметри процесу перед фізичною реалізацією, зменшуючи витратні цикли проб і помилок Siemens Digital Industries Software.

Крім того, перехід до гетерогенної інтеграції та передових технологій упаковки, таких як 3D-складення та архітектури чіплетів, вводить нові виклики для виходу, але також відкриває можливості для оптимізації через покращений контроль процесів та вбудований моніторинг. Оскільки галузь переходить до менших вузлів та складніших архітектур пристроїв, синергія між аналітикою на основі ШІ, передовою інспекцією та цифровим моделюванням процесів буде критично важливою для досягнення вищих виходів прототипів та прискорення виходу на ринок для пристроїв напівпровідників наступного покоління.

Висновок: Найкращі практики для підтримки відмінності виходу прототипів

Досягнення та підтримка високого виходу прототипів у виробництві напівпровідників вимагає цілісного та дисциплінованого підходу, що інтегрує як технічні, так і організаційні найкращі практики. По-перше, надійний збір даних та аналітика є суттєвими; використання передового контролю процесів (APC) та моніторингу в реальному часі дозволяє швидко виявляти та коригувати фактори, що знижують вихід. Впровадження принципів проектування для виробництва (DfM) на ранніх етапах дизайну забезпечує, щоб прототипи були вроджено більш стійкими до варіацій процесу, зменшуючи ризик систематичних дефектів. Крос-функціональна співпраця між командами дизайну, процесу та тестування сприяє культурі безперервного поліпшення та швидкого зворотного зв’язку, що є критично важливим для оптимізації виходу на ранніх стадіях.

Регулярний аналіз кореневих причин із використанням статистичного контролю процесів (SPC) та інструментів аналізу відмов допомагає точно виявляти та усувати джерела втрати виходу. Прийняття проактивного підходу до обслуговування та калібрування обладнання мінімізує непередбачуваний час простою та зсуви процесу, які можуть негативно вплинути на вихід. Крім того, інвестування в навчання персоналу забезпечує, щоб працівники мали найновіші знання та навички для роботи з еволюціонуючими складнощами процесу. Нарешті, порівняння з галузевими стандартами та участь у консорціумах або платформах обміну знаннями, таких як ті, що організовуються SEMI та imec, можуть надати цінні відомості про нові найкращі практики та технології.

Систематично застосовуючи ці найкращі практики, виробники напівпровідників можуть не лише оптимізувати вихід прототипів, але й закласти основу для підтримки відмінності в процесі переходу від прототипування до масового виробництва.

Джерела та посилання

- IEEE (Інститут інженерів електротехніки та електроніки)

- Texas Instruments

- KLA Corporation

- Siemens Digital Industries Software

- imec