半導体製造におけるプロトタイプ歩留まり最適化:最先端技術が初期段階の生産を革新し、競争優位を推進する方法

- はじめに:半導体成功におけるプロトタイプ歩留まりの重要な役割

- 高いプロトタイプ歩留まりを達成するための主要な課題

- 高度なプロセス制御とモニタリング技術

- データ駆動型アプローチ:AIと機械学習を活用した歩留まり改善

- 製造性を考慮した設計:早期に歩留まりの考慮を統合する

- 根本原因分析と欠陥削減戦略

- ケーススタディ:プロトタイプ歩留まり最適化における実世界の成功事例

- 将来のトレンド:歩留まり向上を形作る新興技術

- 結論:持続的なプロトタイプ歩留まり優秀性のためのベストプラクティス

- 出典 & 参考文献

はじめに:半導体成功におけるプロトタイプ歩留まりの重要な役割

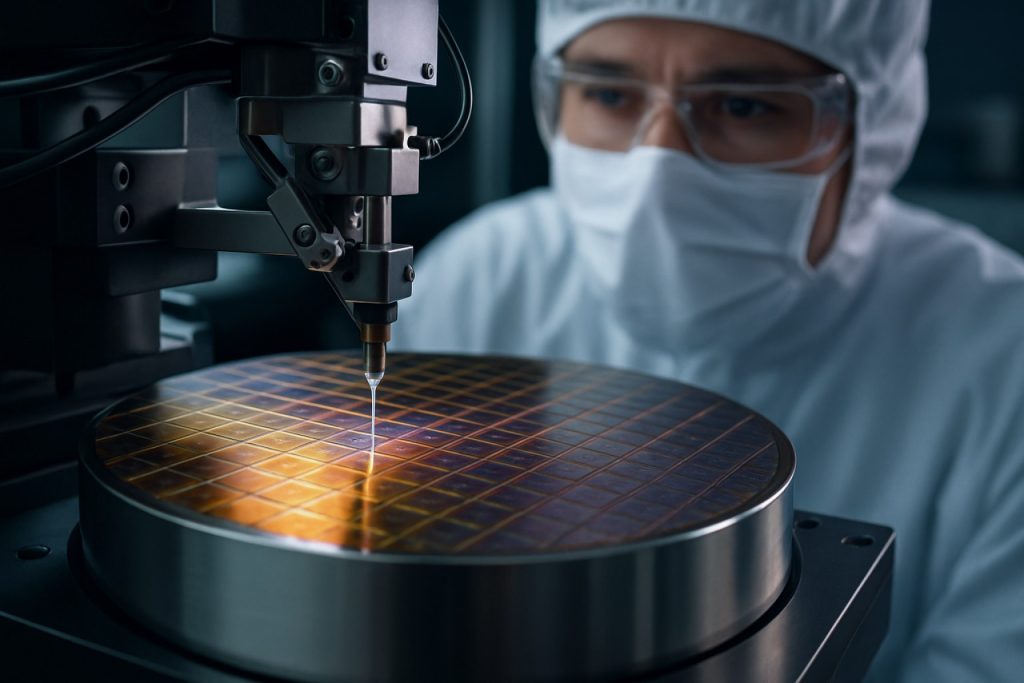

半導体製造の厳しい競争環境において、プロトタイプ段階で達成される歩留まりは、新しいデバイスの技術的および商業的な実現可能性を決定する重要な要素です。プロトタイプ歩留まりは、初期バッチのウェハから生産された機能的なチップの割合を指し、プロセスの成熟度と設計の堅牢性の重要な指標となります。高いプロトタイプ歩留まりは市場投入までの時間を短縮し、開発コストを削減し、量産の成功可能性を高めますが、低い歩留まりは製品の発売や収益性を危うくする根本的な設計やプロセスの問題を示す可能性があります。

デバイスアーキテクチャがますます複雑化し、特徴サイズがナノメートルスケールに縮小するにつれて、プロトタイプ歩留まりの最適化の重要性は高まっています。設計上の欠陥、プロセスの変動、材料の欠陥など、歩留まりを損なう要因を早期に特定し、軽減することが、コストのかかる反復や遅延を避けるために不可欠です。高度な歩留まり分析ツール、データ駆動型プロセス制御、および設計と製造チーム間の密接なコラボレーションは、プロトタイプ歩留まりを最大化し、量産への円滑な移行を確保するための標準的な実践となっています。台湾半導体製造会社(TSMC)によって強調されているように、早期の歩留まり学習は製造効率を改善するだけでなく、設計最適化とプロセスの洗練のための貴重なフィードバックを提供します。

最終的に、プロトタイプ歩留まりを最適化する能力は、半導体企業にとっての重要な差別化要因であり、製品の品質、コスト構造、市場競争力に直接影響を与えます。業界が技術の限界を押し広げ続ける中、プロトタイプ歩留まりの最適化に戦略的に焦点を当てることは、イノベーションと商業的成功を達成するための中心的な要素であり続けるでしょう。

高いプロトタイプ歩留まりを達成するための主要な課題

半導体製造における高いプロトタイプ歩留まりを達成することは、高容量生産で直面する課題とは異なる独自の課題に満ちています。主な障害の一つはプロセスの変動であり、これはプロトタイピング段階での頻繁な設計変更、未成熟なプロセスレシピ、限られた統計的プロセス制御によってより顕著になります。これらの要因は、デバイスの性能の不一致や欠陥率の増加を引き起こし、コスト効率の良い開発に必要な歩留まり目標を達成することを困難にします SEMI。

もう一つの重要な課題は、テスト構造とモニタリングデータの限られた利用可能性です。成熟した生産ラインとは異なり、プロトタイプランでは、包括的なインラインメトロロジーや欠陥検査のカバレッジがしばしば欠けており、迅速な根本原因分析や是正措置を妨げています。このデータの不足は、リソグラフィーの不整合、エッチングプロファイルの偏差、または汚染イベントなど、体系的な歩留まり損失要因の特定を遅らせる可能性があります TSMC。

さらに、プロトタイプにおける新材料やデバイスアーキテクチャの統合は、予期しない故障メカニズムを導入します。これには、プロセス誘発応力に対する感度の増加、新しいインターフェース欠陥、またはプロセスステップ間の予期しない相互作用が含まれます。これらの革新に関する歴史的な故障データの不足は、歩留まりの学習と最適化をさらに複雑にします Intel。

最後に、市場投入までの圧力は、しばしば開発サイクルを加速させ、徹底的なプロセス特性評価と最適化の機会を減少させます。これにより、最適でないプロセスウィンドウや初期の欠陥密度の増加が生じ、重要なプロトタイピング段階での歩留まり改善の努力にさらなる課題をもたらします。

高度なプロセス制御とモニタリング技術

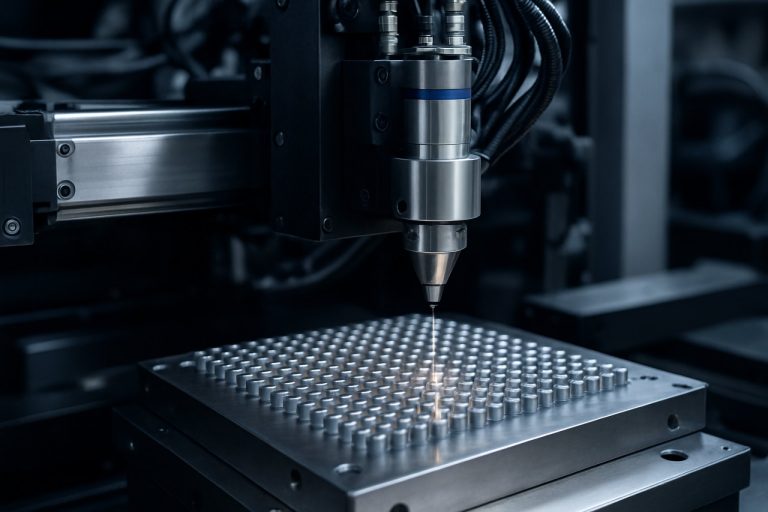

高度なプロセス制御(APC)とモニタリング技術は、半導体製造におけるプロトタイプ歩留まりの最適化において重要な役割を果たします。初期段階のプロセスの変動はデバイス性能やコストに大きな影響を与える可能性があります。APCシステムは、リアルタイムデータ取得をフィードバックおよびフィードフォワード制御戦略と統合し、プロセスパラメータを厳しい許容範囲内に維持することで、欠陥率を低下させ、歩留まりを向上させます。これらのシステムは、センサー、メトロロジーツール、および機械学習アルゴリズムを活用して、逸脱を検出し、最終製品に現れる前に潜在的な歩留まり損失要因を予測します。

主要なモニタリング技術には、重要な寸法、フィルム厚さ、オーバーレイ精度について即時のフィードバックを提供するインラインメトロロジーや、異常のために設備やプロセス信号を継続的に分析する故障検出および分類(FDC)システムが含まれます。統計的プロセス制御(SPC)および仮想メトロロジーを実装することにより、製造業者は従来のエンドオブライン検査では明らかでない微妙なプロセスドリフトや設備の故障を特定できます。この積極的なアプローチにより、迅速な是正措置が可能となり、後続のプロセスステップを通じて欠陥の拡散を最小限に抑えます。

最近のAPCの進展には、人工知能やビッグデータ分析の統合が含まれており、予測メンテナンスや適応プロセス調整を可能にします。これらの技術は、特に複雑で多段階のプロトタイプ製造において、歩留まり損失の根本原因を迅速に特定するのを助けます。その結果、製造業者は高い初回歩留まりを達成し、サイクルタイムを短縮し、プロトタイプから量産への移行を加速できます。詳細については、SEMIやApplied Materialsのリソースを参照してください。

データ駆動型アプローチ:AIと機械学習を活用した歩留まり改善

データ駆動型アプローチ、特に人工知能(AI)や機械学習(ML)を活用したものは、半導体製造におけるプロトタイプ歩留まりの最適化を変革しています。プロセス、設備、およびテストデータの膨大な量を活用することで、AI/MLモデルは、従来の統計手法では見逃されがちな微妙なパターンや相関関係を特定できます。これらの洞察は、歩留まり損失要因の早期発見、根本原因分析、予測メンテナンスを可能にし、すべてがプロトタイプ歩留まりの改善に不可欠です。

重要な応用の一つは、プロセスパラメータやインラインメトロロジーデータに基づいてウェハまたはダイの歩留まりを予測するための教師あり学習アルゴリズムの使用です。歴史的データに基づいてモデルを訓練することで、製造業者は新しいプロトタイプの歩留まり結果を予測し、リスクを軽減するためにプロセス設定を事前に調整できます。クラスタリングや異常検出などの教師なし学習技術は、製造プロセスにおける以前は知られていなかった変動源や外れ値の挙動を明らかにし、ターゲットを絞った是正措置を可能にします。

深層学習によって駆動されるAIベースの欠陥分類システムは、高解像度の検査画像を迅速に分析し、良性の欠陥と歩留まりを制限する欠陥を区別することができ、誤検出を減らし、根本原因の特定を加速します。さらに、強化学習は、リアルタイムでプロセス制御戦略を最適化するために探求されており、変化する条件に適応し、初期のプロトタイプラン中の歩留まり損失を最小限に抑えています。

AI/MLの統合は、業界のリーダーやコンソーシアムによって支持されており、SEMIや台湾半導体製造会社(TSMC)などが標準化されたデータ形式や共同分析を提唱しています。データ駆動型の方法論が成熟するにつれて、歩留まりの向上を加速し、高度な半導体プロトタイプの市場投入までの時間を短縮する上で、ますます中心的な役割を果たすと予想されます。

製造性を考慮した設計:早期に歩留まりの考慮を統合する

半導体設計の最初の段階で歩留まりの考慮を統合することは、プロトタイプ歩留まりを最適化するための重要な戦略であり、一般に製造性を考慮した設計(DfM)と呼ばれます。歩留まり中心の思考を設計プロセスに埋め込むことで、エンジニアは潜在的な製造上の課題に積極的に対処し、コストのかかる反復を減らし、市場投入までの時間を短縮できます。DfMは、設計とプロセスエンジニアリングチーム間の密接なコラボレーションを含み、レイアウト依存効果、プロセスの変動、欠陥感度など、歩留まり損失の原因を特定し、軽減します。

主要なDfMの実践には、リソグラフィーの制約、重要寸法の制御、およびプロセスウィンドウの変動を考慮した高度な設計ルールの使用が含まれます。例えば、レイアウトの規則性や冗長性を取り入れることで欠陥耐性を高めることができ、系統的な欠陥に対して脆弱な重要領域は、慎重なフロアプランニングやルーティングを通じて最小化できます。さらに、シミュレーションツールや予測モデルを使用して、物理的なプロトタイプが製造される前に設計選択の製造性を評価し、歩留まり損失要因を早期に特定することができます。

DfM手法の採用は、特にデバイスのジオメトリが縮小し、プロセスの複雑さが増す中で、初回歩留まりを大幅に改善することが示されています。SEMI(半導体製造装置と材料国際)やIEEE(電気電子技術者協会)などが提供する業界標準やガイドラインは、半導体開発ライフサイクルにDfMを統合するためのフレームワークを提供します。最終的に、DfMを通じた早期の歩留まり最適化は、プロトタイプの成功率を高めるだけでなく、製造コストの削減や製品の信頼性の向上にも寄与します。

根本原因分析と欠陥削減戦略

根本原因分析(RCA)は、半導体製造におけるプロトタイプ歩留まりを最適化する上での基盤であり、歩留まり損失に寄与する根本的な要因を体系的に特定し、対処します。半導体プロセスの複雑さは、フォトリソグラフィー、エッチング、堆積、パッケージングにわたるため、欠陥は設備の故障、材料の不純物、プロセスの変動、人為的エラーなど、さまざまな要因から発生する可能性があります。効果的なRCAは、統計的プロセス制御(SPC)、故障モードおよび影響分析(FMEA)、高度なデータ分析の組み合わせを使用して、欠陥の発生源を追跡し、ターゲットを絞った是正措置を可能にします。

欠陥削減戦略は、RCAから得られた洞察に密接に関連しています。例えば、再発する粒子汚染が特定のツールやプロセスステップに起因することが特定された場合、製造業者は集中メンテナンススケジュールを実施したり、フィルトレーションシステムをアップグレードしたり、プロセスレシピを変更して問題を軽減できます。さらに、リアルタイムモニタリングと機械学習アルゴリズムの採用により、プロセスのドリフトや異常の早期検出が可能になり、歩留まりに影響を与える欠陥の発生率をさらに低下させます。プロセスエンジニア、設備技術者、品質保証スペシャリストを含むクロスファンクショナルチームが協力して是正措置を実施および検証し、改善が次回のプロトタイプランにわたって持続されることを保証します。

Six Sigmaや総合的品質管理(TQM)などの継続的改善フレームワークは、欠陥削減イニシアチブに統合されることが多く、積極的な問題解決とデータ駆動型の意思決定の文化を育成します。根本原因に体系的に対処し、堅牢な欠陥削減戦略を展開することで、半導体製造業者はプロトタイプ歩留まりを大幅に向上させ、市場投入までの時間を短縮し、開発コストを削減できます。これについては、SEMIやテキサス・インスツルメンツが強調しています。

ケーススタディ:プロトタイプ歩留まり最適化における実世界の成功事例

いくつかの半導体製造業者は、高度な分析、プロセス制御、およびクロスファンクショナルコラボレーションの統合を通じて、プロトタイプ歩留まりの最適化において重要な改善を達成しています。例えば、インテル社は、初期のプロセス開発段階で欠陥パターンを分析し、歩留まりを制限する要因を予測するために機械学習アルゴリズムを実装しました。このアプローチにより、根本原因の迅速な特定と軽減が可能となり、新しいプロセスノードにおいて初回歩留まりが15%向上したと報告されています。

同様に、台湾半導体製造会社(TSMC)は、パイロットラインでリアルタイムの統計的プロセス制御(SPC)と自動フィードバックループを採用しました。重要なプロセスパラメータを継続的に監視し、それを電気テスト結果と相関させることで、TSMCはプロトタイプのサイクルタイムを短縮し、歩留まりの向上を図り、高度な技術の市場投入までの時間を短縮しました。

もう一つの注目すべき例は、サムスン電子がデジタルツインと仮想製造モデルを活用してプロセスの変動をシミュレートし、製造性を考慮した設計(DFM)戦略を最適化したことです。このデジタルファーストのアプローチにより、サムスンは物理的なプロトタイピングの前に潜在的な歩留まり損失要因に積極的に対処し、初期歩留まりの向上と開発コストの削減を実現しました。

これらのケーススタディは、データ駆動型の方法論、早期の欠陥検出、および学際的なチームワークの価値を強調しています。業界のリーダーの成功は、高度なプロセス制御と予測分析への投資が、半導体製造における歩留まり、コスト効率、製品品質の測定可能な改善をもたらすことを示しています。

将来のトレンド:歩留まり向上を形作る新興技術

半導体製造におけるプロトタイプ歩留まりの最適化の未来は、欠陥検出、プロセス制御、およびデータ分析を革命的に変える新興技術の融合によって形作られています。最も重要なトレンドの一つは、人工知能(AI)と機械学習(ML)の歩留まり管理システムへの統合です。これらの技術は、ウェハ製造中に生成される膨大なデータセットのリアルタイム分析を可能にし、予測メンテナンス、迅速な根本原因分析、および歩留まり損失を最小限に抑える適応型プロセス調整を実現します 台湾半導体製造会社。

もう一つの変革的な発展は、高解像度の電子ビームおよび光学検査システムなどの高度なメトロロジーおよび検査ツールの採用です。これらのツールは、ナノメートル以下の欠陥に対する前例のない感度を提供し、プロトタイピング段階での歩留まりを制限する異常の早期検出と分類を可能にします KLA Corporation。さらに、製造プロセスの仮想レプリカであるデジタルツインを使用することで、エンジニアは物理的な実装の前にプロセスパラメータをシミュレートおよび最適化でき、コストのかかる試行錯誤サイクルを減少させます Siemens Digital Industries Software。

さらに、3Dスタッキングやチップレットアーキテクチャなどの異種統合および高度なパッケージング技術への移行は、新しい歩留まりの課題をもたらす一方で、プロセス制御やインラインモニタリングの改善を通じて最適化の機会も提供します。業界がより小さなノードやより複雑なデバイスアーキテクチャに向かう中で、AI駆動の分析、高度な検査、デジタルプロセスモデリングの相乗効果は、より高いプロトタイプ歩留まりを達成し、次世代半導体デバイスの市場投入までの時間を加速するために重要です。

結論:持続的なプロトタイプ歩留まり優秀性のためのベストプラクティス

半導体製造において高いプロトタイプ歩留まりを達成し、維持するためには、技術的および組織的なベストプラクティスを統合した全体的で規律あるアプローチが必要です。まず、堅牢なデータ収集と分析が不可欠です。高度なプロセス制御(APC)とリアルタイムモニタリングを活用することで、歩留まり損失要因の迅速な特定と修正が可能となります。設計段階の初期に製造性を考慮した設計(DfM)原則を実装することで、プロトタイプがプロセスの変動に対して本質的により堅牢になり、系統的な欠陥のリスクが減少します。設計、プロセス、およびテストエンジニアリングチーム間のクロスファンクショナルなコラボレーションは、継続的改善と迅速なフィードバックの文化を育み、初期段階の歩留まり最適化にとって重要です。

統計的プロセス制御(SPC)や故障分析ツールを使用した定期的な根本原因分析は、歩留まり損失の原因を特定し、軽減するのに役立ちます。設備のメンテナンスやキャリブレーションに対する積極的なアプローチを採用することで、計画外のダウンタイムやプロセスのドリフトを最小限に抑え、これらは歩留まりに悪影響を及ぼす可能性があります。さらに、労働力のトレーニングに投資することで、スタッフが進化するプロセスの複雑さに対処するための最新の知識とスキルを持つことが保証されます。最後に、業界標準に対するベンチマークを行い、SEMIやimecなどが促進するコンソーシアムや知識共有プラットフォームに参加することで、新興のベストプラクティスや技術に関する貴重な洞察を得ることができます。

これらのベストプラクティスを体系的に適用することで、半導体製造業者はプロトタイプ歩留まりを最適化するだけでなく、プロダクトがプロトタイプから高容量生産に移行する際の持続的な優秀性の基盤を確立できます。