Prototype Yield Optimization in Semiconductor Manufacturing: How Cutting-Edge Techniques Are Revolutionizing Early-Stage Production and Driving Competitive Advantage

- Introduction: The Critical Role of Prototype Yield in Semiconductor Success

- Key Challenges in Achieving High Prototype Yields

- Advanced Process Control and Monitoring Techniques

- Data-Driven Approaches: Leveraging AI and Machine Learning for Yield Improvement

- Design for Manufacturability: Integrating Yield Considerations Early

- Root Cause Analysis and Defect Reduction Strategies

- Case Studies: Real-World Successes in Prototype Yield Optimization

- Future Trends: Emerging Technologies Shaping Yield Enhancement

- Conclusion: Best Practices for Sustained Prototype Yield Excellence

- Sources & References

Introduction: The Critical Role of Prototype Yield in Semiconductor Success

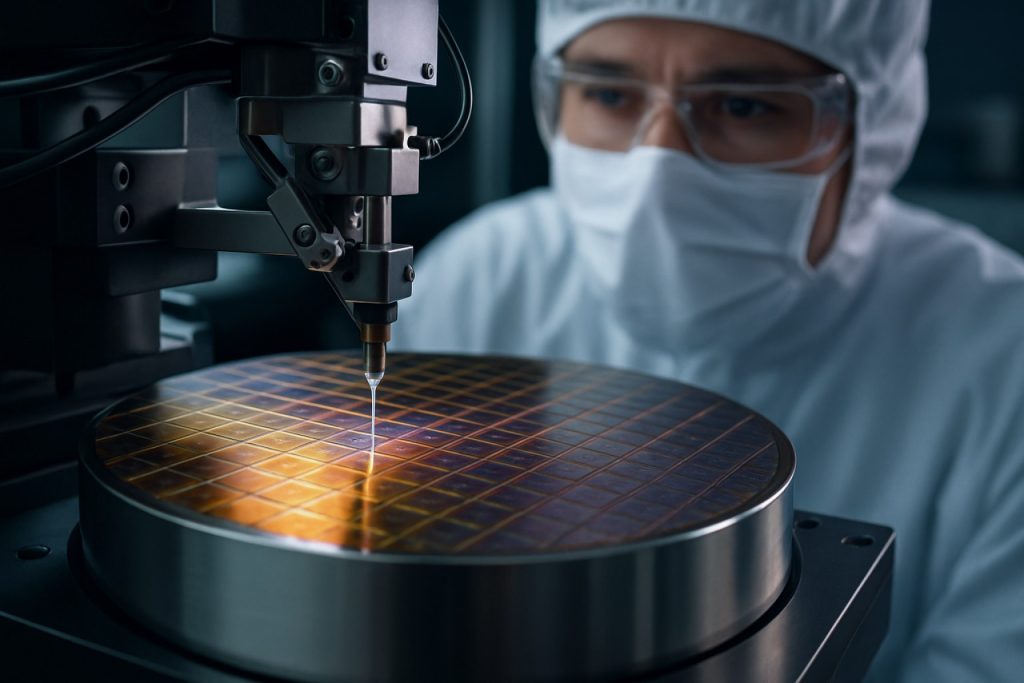

In the fiercely competitive landscape of semiconductor manufacturing, the yield achieved during the prototype phase is a decisive factor in determining both the technical and commercial viability of new devices. Prototype yield refers to the proportion of functional chips produced from an initial batch of wafers, serving as a crucial indicator of process maturity and design robustness. High prototype yield accelerates time-to-market, reduces development costs, and enhances the likelihood of successful mass production, while low yield can signal fundamental design or process issues that may jeopardize a product’s launch or profitability.

The importance of optimizing prototype yield has grown as device architectures become more complex and feature sizes shrink to the nanometer scale. Early identification and mitigation of yield detractors—such as design flaws, process variability, and material defects—are essential to avoid costly iterations and delays. Advanced yield analysis tools, data-driven process control, and close collaboration between design and manufacturing teams are now standard practices to maximize prototype yield and ensure a smooth transition to volume production. As highlighted by Taiwan Semiconductor Manufacturing Company (TSMC), early yield learning not only improves manufacturing efficiency but also provides valuable feedback for design optimization and process refinement.

Ultimately, the ability to optimize prototype yield is a key differentiator for semiconductor companies, directly impacting product quality, cost structure, and market competitiveness. As the industry continues to push the boundaries of technology, the strategic focus on prototype yield optimization will remain central to achieving innovation and commercial success.

Key Challenges in Achieving High Prototype Yields

Achieving high prototype yields in semiconductor manufacturing is fraught with unique challenges that differ from those encountered in high-volume production. One of the primary obstacles is process variability, which is more pronounced during the prototyping phase due to frequent design changes, immature process recipes, and limited statistical process control. These factors can lead to inconsistent device performance and increased defect rates, making it difficult to achieve the yield targets necessary for cost-effective development SEMI.

Another significant challenge is the limited availability of test structures and monitoring data. Unlike mature production lines, prototype runs often lack comprehensive in-line metrology and defect inspection coverage, impeding rapid root-cause analysis and corrective action. This scarcity of data can delay the identification of systematic yield detractors, such as lithography misalignment, etch profile deviations, or contamination events TSMC.

Additionally, the integration of new materials and device architectures in prototypes introduces unforeseen failure mechanisms. These may include increased sensitivity to process-induced stress, novel interface defects, or unexpected interactions between process steps. The lack of historical failure data for these innovations further complicates yield learning and optimization Intel.

Finally, time-to-market pressures often force accelerated development cycles, reducing the opportunity for thorough process characterization and optimization. This can result in suboptimal process windows and higher initial defect densities, further challenging yield improvement efforts during the critical prototyping stage.

Advanced Process Control and Monitoring Techniques

Advanced process control (APC) and monitoring techniques are pivotal in optimizing prototype yield during semiconductor manufacturing, where early-stage process variability can significantly impact device performance and cost. APC systems integrate real-time data acquisition with feedback and feedforward control strategies to maintain process parameters within tight tolerances, thereby reducing defect rates and enhancing yield. These systems leverage sensors, metrology tools, and machine learning algorithms to detect deviations and predict potential yield detractors before they manifest in the final product.

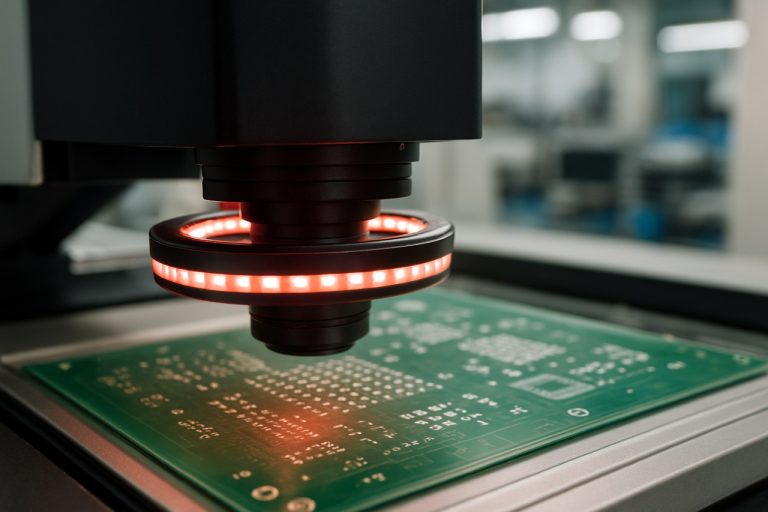

Key monitoring techniques include in-line metrology, which provides immediate feedback on critical dimensions, film thickness, and overlay accuracy, and fault detection and classification (FDC) systems that continuously analyze equipment and process signals for anomalies. By implementing statistical process control (SPC) and virtual metrology, manufacturers can identify subtle process drifts and equipment malfunctions that may not be apparent through traditional end-of-line inspection. This proactive approach enables rapid corrective actions, minimizing the propagation of defects through subsequent process steps.

Recent advancements in APC involve the integration of artificial intelligence and big data analytics, allowing for predictive maintenance and adaptive process tuning. These technologies facilitate the rapid identification of root causes for yield loss, especially in the context of complex, multi-step prototype fabrication. As a result, manufacturers can achieve higher first-pass yield, reduce cycle time, and accelerate the transition from prototype to volume production. For further details, refer to resources from SEMI and Applied Materials.

Data-Driven Approaches: Leveraging AI and Machine Learning for Yield Improvement

Data-driven approaches, particularly those leveraging artificial intelligence (AI) and machine learning (ML), are transforming prototype yield optimization in semiconductor manufacturing. By harnessing vast amounts of process, equipment, and test data, AI/ML models can identify subtle patterns and correlations that traditional statistical methods may overlook. These insights enable early detection of yield detractors, root cause analysis, and predictive maintenance, all of which are critical for improving prototype yields.

One key application is the use of supervised learning algorithms to predict wafer or die yield based on process parameters and in-line metrology data. By training models on historical data, manufacturers can forecast yield outcomes for new prototypes and proactively adjust process settings to mitigate risks. Unsupervised learning techniques, such as clustering and anomaly detection, help uncover previously unknown sources of variation or outlier behavior in the fabrication process, enabling targeted corrective actions.

AI-driven defect classification systems, powered by deep learning, can rapidly analyze high-resolution inspection images to distinguish between benign and yield-limiting defects, reducing false positives and accelerating root cause identification. Additionally, reinforcement learning is being explored to optimize process control strategies in real time, adapting to changing conditions and minimizing yield loss during early prototype runs.

The integration of AI/ML into yield management platforms is supported by industry leaders and consortia, such as SEMI and Taiwan Semiconductor Manufacturing Company (TSMC), who advocate for standardized data formats and collaborative analytics. As data-driven methodologies mature, they are expected to play an increasingly central role in accelerating yield ramp and reducing time-to-market for advanced semiconductor prototypes.

Design for Manufacturability: Integrating Yield Considerations Early

Integrating yield considerations at the earliest stages of semiconductor design—commonly referred to as Design for Manufacturability (DfM)—is a critical strategy for optimizing prototype yield. By embedding yield-centric thinking into the design process, engineers can proactively address potential manufacturing challenges, reducing costly iterations and accelerating time-to-market. DfM involves close collaboration between design and process engineering teams to identify and mitigate sources of yield loss, such as layout-dependent effects, process variability, and defect sensitivity.

Key DfM practices include the use of advanced design rules that account for lithography limitations, critical dimension control, and process window variability. For example, layout regularity and redundancy can be incorporated to enhance defect tolerance, while critical areas prone to systematic defects can be minimized through careful floorplanning and routing. Additionally, simulation tools and predictive models are employed to assess the manufacturability of design choices before physical prototypes are fabricated, allowing for early detection of yield detractors.

The adoption of DfM methodologies has been shown to significantly improve first-pass yield, especially as device geometries shrink and process complexity increases. Industry standards and guidelines, such as those provided by the SEMI (Semiconductor Equipment and Materials International) and IEEE (Institute of Electrical and Electronics Engineers), offer frameworks for integrating DfM into the semiconductor development lifecycle. Ultimately, early yield optimization through DfM not only enhances prototype success rates but also contributes to lower production costs and improved product reliability.

Root Cause Analysis and Defect Reduction Strategies

Root cause analysis (RCA) is a cornerstone in optimizing prototype yield within semiconductor manufacturing, as it systematically identifies and addresses the underlying factors contributing to yield loss. The complexity of semiconductor processes—spanning photolithography, etching, deposition, and packaging—means that defects can originate from a multitude of sources, including equipment malfunctions, material impurities, process variations, and human error. Effective RCA employs a combination of statistical process control (SPC), failure mode and effects analysis (FMEA), and advanced data analytics to trace defects back to their origin, enabling targeted corrective actions.

Defect reduction strategies are closely tied to the insights gained from RCA. For instance, once a recurring particle contamination is traced to a specific tool or process step, manufacturers can implement focused maintenance schedules, upgrade filtration systems, or modify process recipes to mitigate the issue. Additionally, the adoption of real-time monitoring and machine learning algorithms allows for early detection of process drifts and anomalies, further reducing the incidence of yield-impacting defects. Cross-functional teams, including process engineers, equipment technicians, and quality assurance specialists, collaborate to implement and validate corrective measures, ensuring that improvements are sustained over subsequent prototype runs.

Continuous improvement frameworks such as Six Sigma and Total Quality Management (TQM) are often integrated into defect reduction initiatives, fostering a culture of proactive problem-solving and data-driven decision-making. By systematically addressing root causes and deploying robust defect reduction strategies, semiconductor manufacturers can significantly enhance prototype yield, accelerate time-to-market, and reduce development costs, as highlighted by SEMI and Texas Instruments.

Case Studies: Real-World Successes in Prototype Yield Optimization

Several semiconductor manufacturers have achieved significant improvements in prototype yield optimization through the integration of advanced analytics, process control, and cross-functional collaboration. For instance, Intel Corporation implemented machine learning algorithms to analyze defect patterns and predict yield-limiting factors during the early stages of process development. This approach enabled rapid identification and mitigation of root causes, resulting in a reported 15% increase in first-pass yield for new process nodes.

Similarly, Taiwan Semiconductor Manufacturing Company (TSMC) adopted real-time statistical process control (SPC) and automated feedback loops in their pilot lines. By continuously monitoring critical process parameters and correlating them with electrical test results, TSMC reduced prototype cycle times and improved yield ramp rates, accelerating time-to-market for advanced technologies.

Another notable example is Samsung Electronics, which leveraged digital twins and virtual fabrication models to simulate process variations and optimize design-for-manufacturability (DFM) strategies. This digital-first approach allowed Samsung to proactively address potential yield detractors before physical prototyping, leading to higher initial yields and reduced development costs.

These case studies underscore the value of data-driven methodologies, early defect detection, and cross-disciplinary teamwork in achieving prototype yield optimization. The successes of industry leaders demonstrate that investing in advanced process control and predictive analytics can deliver measurable improvements in yield, cost efficiency, and product quality in semiconductor manufacturing.

Future Trends: Emerging Technologies Shaping Yield Enhancement

The future of prototype yield optimization in semiconductor manufacturing is being shaped by a convergence of emerging technologies that promise to revolutionize defect detection, process control, and data analytics. One of the most significant trends is the integration of artificial intelligence (AI) and machine learning (ML) into yield management systems. These technologies enable real-time analysis of vast datasets generated during wafer fabrication, allowing for predictive maintenance, rapid root-cause analysis, and adaptive process adjustments that minimize yield loss Taiwan Semiconductor Manufacturing Company.

Another transformative development is the adoption of advanced metrology and inspection tools, such as high-resolution e-beam and optical inspection systems. These tools provide unprecedented sensitivity to sub-nanometer defects, enabling earlier detection and classification of yield-limiting anomalies during the prototyping phase KLA Corporation. Additionally, the use of digital twins—virtual replicas of manufacturing processes—allows engineers to simulate and optimize process parameters before physical implementation, reducing costly trial-and-error cycles Siemens Digital Industries Software.

Furthermore, the transition to heterogeneous integration and advanced packaging technologies, such as 3D stacking and chiplet architectures, introduces new yield challenges but also opportunities for optimization through improved process control and in-line monitoring. As the industry moves toward smaller nodes and more complex device architectures, the synergy between AI-driven analytics, advanced inspection, and digital process modeling will be critical in achieving higher prototype yields and accelerating time-to-market for next-generation semiconductor devices.

Conclusion: Best Practices for Sustained Prototype Yield Excellence

Achieving and maintaining high prototype yield in semiconductor manufacturing requires a holistic and disciplined approach, integrating both technical and organizational best practices. First, robust data collection and analytics are essential; leveraging advanced process control (APC) and real-time monitoring enables rapid identification and correction of yield detractors. Implementing Design for Manufacturability (DfM) principles early in the design phase ensures that prototypes are inherently more robust to process variations, reducing the risk of systematic defects. Cross-functional collaboration between design, process, and test engineering teams fosters a culture of continuous improvement and rapid feedback, which is critical for early-stage yield optimization.

Regular root cause analysis using statistical process control (SPC) and failure analysis tools helps in pinpointing and mitigating sources of yield loss. Adopting a proactive approach to equipment maintenance and calibration minimizes unplanned downtime and process drift, both of which can negatively impact yield. Furthermore, investing in workforce training ensures that personnel are equipped with the latest knowledge and skills to handle evolving process complexities. Finally, benchmarking against industry standards and participating in consortia or knowledge-sharing platforms, such as those facilitated by SEMI and imec, can provide valuable insights into emerging best practices and technologies.

By systematically applying these best practices, semiconductor manufacturers can not only optimize prototype yield but also establish a foundation for sustained excellence as products transition from prototyping to high-volume production.

Sources & References

- IEEE (Institute of Electrical and Electronics Engineers)

- Texas Instruments

- KLA Corporation

- Siemens Digital Industries Software

- imec