Prototypen-Ausbeute-Optimierung in der Halbleiterfertigung: Wie modernste Techniken die Produktion in der Frühphase revolutionieren und einen Wettbewerbsvorteil schaffen

- Einführung: Die entscheidende Rolle der Prototypen-Ausbeute im Halbleitererfolg

- Herausforderungen bei der Erreichung hoher Prototypen-Ausbeuten

- Fortgeschrittene Prozesskontroll- und Überwachungstechniken

- Datengetriebene Ansätze: Nutzung von KI und maschinellem Lernen zur Verbesserung der Ausbeute

- Design for Manufacturability: Integration von Ausbeutebetrachtungen in der frühen Phase

- Ursachenanalyse und Strategien zur Defektreduzierung

- Fallstudien: Erfolge in der Prototypen-Ausbeute-Optimierung in der Praxis

- Zukünftige Trends: Aufkommende Technologien zur Verbesserung der Ausbeute

- Fazit: Best Practices für nachhaltige Exzellenz in der Prototypen-Ausbeute

- Quellen & Referenzen

Einführung: Die entscheidende Rolle der Prototypen-Ausbeute im Halbleitererfolg

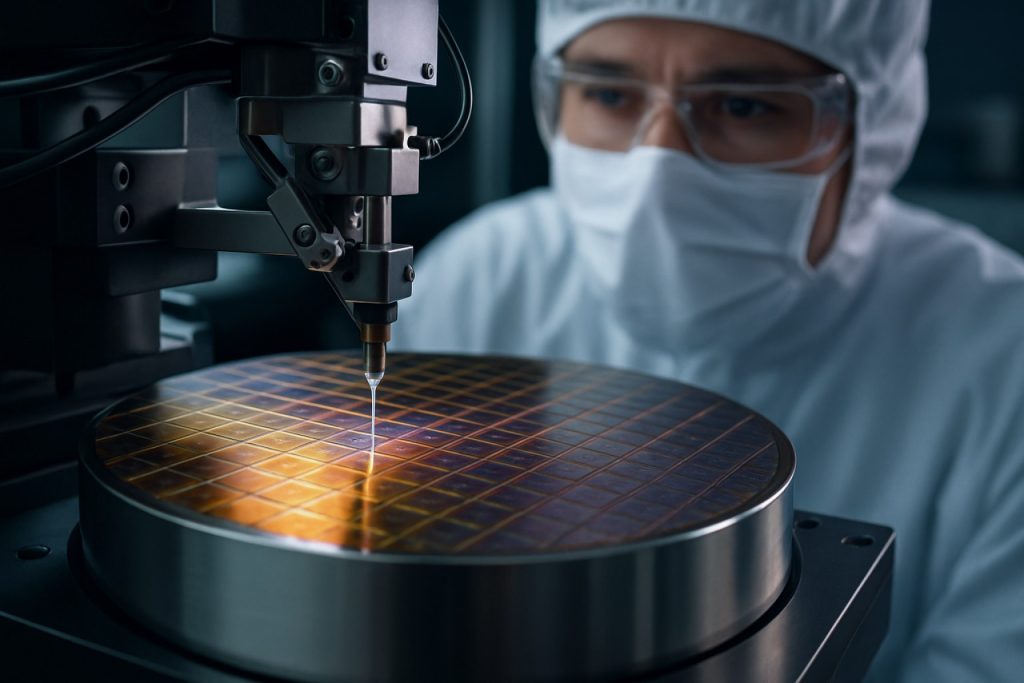

In der hart umkämpften Landschaft der Halbleiterfertigung ist die Ausbeute, die während der Prototypenphase erzielt wird, ein entscheidender Faktor für die technische und kommerzielle Lebensfähigkeit neuer Geräte. Die Prototypen-Ausbeute bezieht sich auf den Anteil funktionierender Chips, die aus einer ersten Charge von Wafern produziert werden, und dient als wichtiger Indikator für die Prozessreife und Robustheit des Designs. Eine hohe Prototypen-Ausbeute beschleunigt die Markteinführungszeit, senkt die Entwicklungskosten und erhöht die Wahrscheinlichkeit einer erfolgreichen Massenproduktion, während eine niedrige Ausbeute auf grundlegende Design- oder Prozessprobleme hinweisen kann, die den Markteintritt oder die Rentabilität eines Produkts gefährden könnten.

Die Bedeutung der Optimierung der Prototypen-Ausbeute ist gewachsen, da die Gerätearchitekturen komplexer werden und die Strukturgrößen auf den Nanometermaßstab schrumpfen. Eine frühzeitige Identifizierung und Minderung von Faktoren, die die Ausbeute beeinträchtigen—wie Designfehler, Prozessvariabilität und Materialfehler—ist entscheidend, um kostspielige Iterationen und Verzögerungen zu vermeiden. Fortschrittliche Werkzeuge zur Ausbeuteanalyse, datengestützte Prozesskontrolle und enge Zusammenarbeit zwischen Design- und Fertigungsteams sind mittlerweile Standardpraktiken, um die Prototypen-Ausbeute zu maximieren und einen reibungslosen Übergang zur Serienproduktion sicherzustellen. Wie die Taiwan Semiconductor Manufacturing Company (TSMC) hervorhebt, verbessert das frühe Lernen über die Ausbeute nicht nur die Fertigungseffizienz, sondern liefert auch wertvolles Feedback für die Designoptimierung und Prozessverfeinerung.

Letztlich ist die Fähigkeit zur Optimierung der Prototypen-Ausbeute ein entscheidender Differenzierungsfaktor für Halbleiterunternehmen, der sich direkt auf die Produktqualität, die Kostenstruktur und die Wettbewerbsfähigkeit auswirkt. Während die Branche weiterhin die Grenzen der Technologie verschiebt, wird der strategische Fokus auf die Optimierung der Prototypen-Ausbeute zentral bleiben, um Innovation und kommerziellen Erfolg zu erzielen.

Herausforderungen bei der Erreichung hoher Prototypen-Ausbeuten

Die Erreichung hoher Prototypen-Ausbeuten in der Halbleiterfertigung ist mit einzigartigen Herausforderungen verbunden, die sich von denen in der Hochvolumenproduktion unterscheiden. Ein wesentliches Hindernis ist die Prozessvariabilität, die während der Prototypenphase aufgrund häufiger Designänderungen, unreifer Prozessrezepte und begrenzter statistischer Prozesskontrolle ausgeprägter ist. Diese Faktoren können zu inkonsistentem Geräteverhalten und erhöhten Defektraten führen, was es schwierig macht, die für eine kosteneffektive Entwicklung erforderlichen Ausbeuteziele zu erreichen SEMI.

Eine weitere bedeutende Herausforderung ist die begrenzte Verfügbarkeit von Teststrukturen und Überwachungsdaten. Im Gegensatz zu ausgereiften Produktionslinien fehlen Prototypenläufe häufig umfassende inline-Metrologie und Defektinspektionsabdeckung, was eine schnelle Ursachenanalyse und Korrekturmaßnahmen erschwert. Diese Datenknappheit kann die Identifizierung systematischer Ausbeute beeinträchtigender Faktoren wie Lithografiemisalignment, Ätzprofilabweichungen oder Kontaminationsereignisse TSMC verzögern.

Zusätzlich führt die Integration neuer Materialien und Gerätearchitekturen in Prototypen zu unvorhergesehenen Fehlermechanismen. Dazu gehören eine erhöhte Empfindlichkeit gegenüber prozessbedingtem Stress, neuartige Schnittstellenfehler oder unerwartete Wechselwirkungen zwischen Prozessschritten. Das Fehlen historischer Fehlerinformationen für diese Innovationen erschwert zudem das Lernen und die Optimierung der Ausbeute Intel.

Schließlich zwingen Zeitdruck und Markteinführungsdruck häufig zu beschleunigten Entwicklungszyklen, wodurch die Möglichkeit einer gründlichen Prozesscharakterisierung und -optimierung verringert wird. Dies kann zu suboptimalen Prozessfenstern und höheren anfänglichen Defektdichten führen, was die Bemühungen zur Verbesserung der Ausbeute während der kritischen Prototypenphase weiter erschwert.

Fortgeschrittene Prozesskontroll- und Überwachungstechniken

Fortgeschrittene Prozesskontroll- (APC) und Überwachungstechniken sind entscheidend für die Optimierung der Prototypen-Ausbeute während der Halbleiterfertigung, wo die Variabilität in der frühen Phase die Geräteleistung und die Kosten erheblich beeinflussen kann. APC-Systeme integrieren die Echtzeit-Datenerfassung mit Feedback- und Feedforward-Kontrollstrategien, um die Prozessparameter innerhalb enger Toleranzen zu halten, wodurch die Defektraten gesenkt und die Ausbeute erhöht wird. Diese Systeme nutzen Sensoren, Metrologie-Tools und Algorithmen des maschinellen Lernens, um Abweichungen zu erkennen und potenzielle Faktoren, die die Ausbeute beeinträchtigen, vorherzusagen, bevor sie im Endprodukt sichtbar werden.

Wichtige Überwachungstechniken umfassen die inline-Metrologie, die sofortiges Feedback zu kritischen Dimensionen, Filmstärken und Überlagerungsgenauigkeit liefert, sowie Fehlererkennungs- und Klassifizierungssysteme (FDC), die kontinuierlich Geräte- und Prozesssignale auf Anomalien analysieren. Durch die Implementierung statistischer Prozesskontrolle (SPC) und virtueller Metrologie können Hersteller subtile Prozessdrifts und Gerätestörungen identifizieren, die möglicherweise nicht durch traditionelle End-of-Line-Inspektionen erkennbar sind. Dieser proaktive Ansatz ermöglicht schnelle Korrekturmaßnahmen und minimiert die Ausbreitung von Defekten durch nachfolgende Prozessschritte.

Neueste Fortschritte in der APC beinhalten die Integration von künstlicher Intelligenz und Big Data-Analytik, die prädiktive Wartung und adaptive Prozessoptimierung ermöglichen. Diese Technologien erleichtern die schnelle Identifizierung der Ursachen für Ausbeuteverluste, insbesondere im Kontext der komplexen, mehrstufigen Prototypenfertigung. Dadurch können Hersteller eine höhere Erstpassausbeute erzielen, die Zykluszeit reduzieren und den Übergang von der Prototypen- zur Serienproduktion beschleunigen. Für weitere Details siehe Ressourcen von SEMI und Applied Materials.

Datengetriebene Ansätze: Nutzung von KI und maschinellem Lernen zur Verbesserung der Ausbeute

Datengetriebene Ansätze, insbesondere solche, die künstliche Intelligenz (KI) und maschinelles Lernen (ML) nutzen, transformieren die Optimierung der Prototypen-Ausbeute in der Halbleiterfertigung. Durch die Nutzung großer Mengen von Prozess-, Geräte- und Testdaten können KI/ML-Modelle subtile Muster und Korrelationen erkennen, die traditionelle statistische Methoden möglicherweise übersehen. Diese Erkenntnisse ermöglichen die frühzeitige Erkennung von Faktoren, die die Ausbeute beeinträchtigen, die Ursachenanalyse und die prädiktive Wartung, die alle entscheidend für die Verbesserung der Prototypen-Ausbeute sind.

Eine wichtige Anwendung ist die Verwendung von überwachten Lernalgorithmen zur Vorhersage der Wafer- oder Die-Ausbeute basierend auf Prozessparametern und inline-Metrologiedaten. Durch das Training von Modellen mit historischen Daten können Hersteller die Ausbeuteergebnisse für neue Prototypen vorhersagen und proaktiv die Prozesseinstellungen anpassen, um Risiken zu mindern. Unüberwachte Lerntechniken, wie Clustering und Anomalieerkennung, helfen, zuvor unbekannte Quellen der Variabilität oder Ausreißer im Fertigungsprozess aufzudecken, was gezielte Korrekturmaßnahmen ermöglicht.

KI-gesteuerte Defektklassifizierungssysteme, die auf tiefem Lernen basieren, können hochauflösende Inspektionsbilder schnell analysieren, um zwischen harmlosen und ausbeute-limitierenden Defekten zu unterscheiden, wodurch falsch-positive Ergebnisse reduziert und die Identifizierung der Ursachen beschleunigt wird. Darüber hinaus wird das Verstärkungslernen untersucht, um Prozesskontrollstrategien in Echtzeit zu optimieren, sich an veränderte Bedingungen anzupassen und den Ausbeuteverlust während der frühen Prototypenläufe zu minimieren.

Die Integration von KI/ML in Ausbeutemanagementplattformen wird von Branchenführern und -konsortien, wie SEMI und der Taiwan Semiconductor Manufacturing Company (TSMC), unterstützt, die sich für standardisierte Datenformate und gemeinsame Analysen einsetzen. Mit dem Fortschritt datengetriebener Methoden wird erwartet, dass sie eine zunehmend zentrale Rolle bei der Beschleunigung der Ausbeute und der Reduzierung der Markteinführungszeit für fortschrittliche Halbleiterprototypen spielen.

Design for Manufacturability: Integration von Ausbeutebetrachtungen in der frühen Phase

Die Integration von Ausbeutebetrachtungen in den frühesten Phasen des Halbleiterdesigns—häufig als Design for Manufacturability (DfM) bezeichnet—ist eine entscheidende Strategie zur Optimierung der Prototypen-Ausbeute. Durch die Einbettung eines ausbeutefokussierten Denkens in den Designprozess können Ingenieure potenzielle Fertigungsherausforderungen proaktiv angehen, kostspielige Iterationen reduzieren und die Markteinführungszeit beschleunigen. DfM beinhaltet eine enge Zusammenarbeit zwischen Design- und Prozessengineering-Teams, um Quellen von Ausbeuteverlusten wie layoutabhängige Effekte, Prozessvariabilität und Defektempfindlichkeit zu identifizieren und zu mindern.

Wichtige DfM-Praktiken umfassen die Verwendung fortschrittlicher Designregeln, die Lithografiebeschränkungen, die Kontrolle kritischer Dimensionen und die Variabilität des Prozessfensters berücksichtigen. Beispielsweise können Layoutregelmäßigkeiten und Redundanzen integriert werden, um die Defektverträglichkeit zu erhöhen, während kritische Bereiche, die anfällig für systematische Defekte sind, durch sorgfältige Floorplanung und Routing minimiert werden können. Darüber hinaus werden Simulationswerkzeuge und prädiktive Modelle eingesetzt, um die Herstellbarkeit von Designentscheidungen zu bewerten, bevor physische Prototypen gefertigt werden, um eine frühzeitige Erkennung von Faktoren, die die Ausbeute beeinträchtigen, zu ermöglichen.

Die Einführung von DfM-Methoden hat gezeigt, dass sie die Erstpassausbeute erheblich verbessern, insbesondere da die Gerätegeometrien schrumpfen und die Prozesskomplexität zunimmt. Branchenstandards und -richtlinien, wie sie von SEMI (Semiconductor Equipment and Materials International) und IEEE (Institute of Electrical and Electronics Engineers) bereitgestellt werden, bieten Rahmenbedingungen für die Integration von DfM in den Entwicklungszyklus von Halbleitern. Letztendlich verbessert die frühzeitige Optimierung der Ausbeute durch DfM nicht nur die Erfolgsquote von Prototypen, sondern trägt auch zu niedrigeren Produktionskosten und verbesserter Produktzuverlässigkeit bei.

Ursachenanalyse und Strategien zur Defektreduzierung

Die Ursachenanalyse (RCA) ist ein Eckpfeiler bei der Optimierung der Prototypen-Ausbeute in der Halbleiterfertigung, da sie systematisch die zugrunde liegenden Faktoren identifiziert und anspricht, die zu Ausbeuteverlusten führen. Die Komplexität der Halbleiterprozesse—die Fotolithografie, Ätzen, Abscheidung und Verpackung umfasst—bedeutet, dass Defekte aus einer Vielzahl von Quellen stammen können, einschließlich Geräteausfällen, Materialverunreinigungen, Prozessvariationen und menschlichem Versagen. Effektive RCA verwendet eine Kombination aus statistischer Prozesskontrolle (SPC), Fehlermuster- und Wirkungsanalyse (FMEA) und fortschrittlicher Datenanalyse, um Defekte bis zu ihrem Ursprung zurückzuverfolgen und gezielte Korrekturmaßnahmen zu ermöglichen.

Strategien zur Defektreduzierung sind eng mit den Erkenntnissen aus der RCA verbunden. Wenn beispielsweise eine wiederkehrende Partikelkontamination auf ein bestimmtes Werkzeug oder einen bestimmten Prozessschritt zurückverfolgt wird, können Hersteller gezielte Wartungspläne umsetzen, Filtrationssysteme aufrüsten oder Prozessrezepte ändern, um das Problem zu mindern. Darüber hinaus ermöglicht die Einführung von Echtzeitüberwachung und Algorithmen des maschinellen Lernens eine frühzeitige Erkennung von Prozessdrifts und Anomalien, wodurch die Inzidenz von ausbeute-beeinträchtigenden Defekten weiter reduziert wird. Interdisziplinäre Teams, einschließlich Prozessingenieuren, Gerätetechnikern und Qualitätssicherungsspezialisten, arbeiten zusammen, um Korrekturmaßnahmen umzusetzen und zu validieren und sicherzustellen, dass Verbesserungen über nachfolgende Prototypenläufe aufrechterhalten werden.

Kontinuierliche Verbesserungsrahmen wie Six Sigma und Total Quality Management (TQM) werden häufig in Initiativen zur Defektreduzierung integriert, um eine Kultur des proaktiven Problemlösens und datengestützten Entscheidens zu fördern. Durch die systematische Bearbeitung von Ursachen und die Implementierung robuster Strategien zur Defektreduzierung können Halbleiterhersteller die Prototypen-Ausbeute erheblich steigern, die Markteinführungszeit beschleunigen und die Entwicklungskosten senken, wie von SEMI und Texas Instruments hervorgehoben.

Fallstudien: Erfolge in der Prototypen-Ausbeute-Optimierung in der Praxis

Mehrere Halbleiterhersteller haben durch die Integration fortschrittlicher Analytik, Prozesskontrolle und interdisziplinärer Zusammenarbeit erhebliche Verbesserungen in der Prototypen-Ausbeute-Optimierung erzielt. Beispielsweise implementierte die Intel Corporation Algorithmen des maschinellen Lernens, um Defektmuster zu analysieren und ausbeute-limitierende Faktoren in den frühen Phasen der Prozessentwicklung vorherzusagen. Dieser Ansatz ermöglichte eine schnelle Identifizierung und Minderung von Ursachen, was zu einem berichteten Anstieg der Erstpassausbeute um 15 % bei neuen Prozessknoten führte.

Ähnlich adoptierte die Taiwan Semiconductor Manufacturing Company (TSMC) in ihren Pilotlinien eine Echtzeit-statistische Prozesskontrolle (SPC) und automatisierte Rückkopplungsschleifen. Durch die kontinuierliche Überwachung kritischer Prozessparameter und deren Korrelation mit elektrischen Testergebnissen reduzierte TSMC die Prototypenzykluszeiten und verbesserte die Ausbeute-Rampenraten, was die Markteinführungszeit für fortschrittliche Technologien beschleunigte.

Ein weiteres bemerkenswertes Beispiel ist Samsung Electronics, das digitale Zwillinge und virtuelle Fertigungsmodelle nutzte, um Prozessvariationen zu simulieren und Strategien für das Design for Manufacturability (DFM) zu optimieren. Dieser digitale Ansatz ermöglichte es Samsung, potenzielle Faktoren, die die Ausbeute beeinträchtigen, proaktiv anzugehen, bevor physische Prototypen erstellt wurden, was zu höheren anfänglichen Ausbeuten und reduzierten Entwicklungskosten führte.

Diese Fallstudien unterstreichen den Wert datengetriebener Methoden, frühzeitiger Defekterkennung und interdisziplinärer Teamarbeit zur Erreichung der Prototypen-Ausbeute-Optimierung. Die Erfolge der Branchenführer zeigen, dass Investitionen in fortschrittliche Prozesskontrolle und prädiktive Analytik messbare Verbesserungen in der Ausbeute, Kosteneffizienz und Produktqualität in der Halbleiterfertigung liefern können.

Zukünftige Trends: Aufkommende Technologien zur Verbesserung der Ausbeute

Die Zukunft der Prototypen-Ausbeute-Optimierung in der Halbleiterfertigung wird durch eine Konvergenz aufkommender Technologien geprägt, die versprechen, die Defekterkennung, Prozesskontrolle und Datenanalyse zu revolutionieren. Einer der bedeutendsten Trends ist die Integration von künstlicher Intelligenz (KI) und maschinellem Lernen (ML) in Ausbeutemanagementsysteme. Diese Technologien ermöglichen die Echtzeitanalyse großer Datensätze, die während der Waferfertigung erzeugt werden, und erlauben prädiktive Wartung, schnelle Ursachenanalysen und adaptive Prozessanpassungen, die den Ausbeuteverlust minimieren Taiwan Semiconductor Manufacturing Company.

Eine weitere transformative Entwicklung ist die Einführung fortschrittlicher Metrologie- und Inspektionswerkzeuge, wie hochauflösende E-Beam- und optische Inspektionssysteme. Diese Werkzeuge bieten eine beispiellose Empfindlichkeit gegenüber sub-nanometergroßen Defekten, was eine frühere Erkennung und Klassifizierung von ausbeute-limitierenden Anomalien während der Prototypenphase ermöglicht KLA Corporation. Darüber hinaus ermöglicht die Nutzung von digitalen Zwillingen—virtuellen Nachbildungen von Fertigungsprozessen—Ingenieuren, Prozessparameter vor der physischen Implementierung zu simulieren und zu optimieren, wodurch kostspielige Versuch-und-Irrtum-Zyklen reduziert werden Siemens Digital Industries Software.

Darüber hinaus führt der Übergang zu heterogener Integration und fortschrittlichen Verpackungstechnologien, wie 3D-Stacking und Chiplet-Architekturen, zu neuen Herausforderungen für die Ausbeute, bietet jedoch auch Möglichkeiten zur Optimierung durch verbesserte Prozesskontrolle und inline-Überwachung. Während die Branche sich in Richtung kleinerer Knoten und komplexerer Gerätearchitekturen bewegt, wird die Synergie zwischen KI-gesteuerten Analysen, fortschrittlicher Inspektion und digitalem Prozessmodellierung entscheidend sein, um höhere Prototypen-Ausbeuten zu erzielen und die Markteinführungszeit für Halbleitergeräte der nächsten Generation zu beschleunigen.

Fazit: Best Practices für nachhaltige Exzellenz in der Prototypen-Ausbeute

Die Erreichung und Aufrechterhaltung einer hohen Prototypen-Ausbeute in der Halbleiterfertigung erfordert einen ganzheitlichen und disziplinierten Ansatz, der sowohl technische als auch organisatorische Best Practices integriert. Zunächst sind robuste Datensammlungen und Analysen unerlässlich; die Nutzung fortschrittlicher Prozesskontrolle (APC) und Echtzeitüberwachung ermöglicht eine schnelle Identifizierung und Korrektur von Faktoren, die die Ausbeute beeinträchtigen. Die frühzeitige Implementierung von Design for Manufacturability (DfM)-Prinzipien in der Designphase stellt sicher, dass Prototypen von Natur aus robuster gegenüber Prozessvariationen sind, wodurch das Risiko systematischer Defekte verringert wird. Die interdisziplinäre Zusammenarbeit zwischen Design-, Prozess- und Testengineering-Teams fördert eine Kultur der kontinuierlichen Verbesserung und schnellen Rückmeldungen, die für die frühzeitige Optimierung der Ausbeute entscheidend ist.

Regelmäßige Ursachenanalysen unter Verwendung statistischer Prozesskontrolle (SPC) und Fehlermusteranalyse-Tools helfen, Quellen von Ausbeuteverlusten zu identifizieren und zu mindern. Ein proaktiver Ansatz für die Wartung und Kalibrierung von Geräten minimiert ungeplante Ausfallzeiten und Prozessdrifts, die beide die Ausbeute negativ beeinflussen können. Darüber hinaus stellt die Investition in die Schulung der Mitarbeiter sicher, dass das Personal mit dem neuesten Wissen und den neuesten Fähigkeiten ausgestattet ist, um mit den sich entwickelnden Prozesskomplexitäten umzugehen. Schließlich können Benchmarking gegen Branchenstandards und die Teilnahme an Konsortien oder Wissensaustauschplattformen, wie sie von SEMI und imec gefördert werden, wertvolle Einblicke in aufkommende Best Practices und Technologien bieten.

Durch die systematische Anwendung dieser Best Practices können Halbleiterhersteller nicht nur die Prototypen-Ausbeute optimieren, sondern auch eine Grundlage für nachhaltige Exzellenz schaffen, während Produkte von der Prototypenphase in die Hochvolumenproduktion übergehen.

Quellen & Referenzen

- IEEE (Institute of Electrical and Electronics Engineers)

- Texas Instruments

- KLA Corporation

- Siemens Digital Industries Software

- imec